# MS90C365

—— 150MHz 的 18bit 平板显示器 (FPD) LVDS 信号发送器

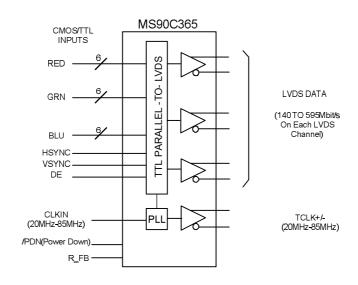

#### 功能概述

MS90C365 芯片能够将 18bit 的 TTL 数据转换成 3 通道的低压差分信号 (LVDS)。时钟通道经过锁相之后与数据通道并行输出。在时钟频率为 150MHz 时,18bit 的 RGB 数据、3bit 的 LCD 时序数据以 1050Mbps 的速率在每个 LVDS 数据通道中传输。输入时钟频率为 150MHz 时,数据的传输速率为 525Mbytes/sec。MS90C365 的 R\_FB 管脚可以选择在时钟的上升沿或者下降沿有效。此款芯片是解决高带宽、高速 TTL 信号层面的电磁干扰和电缆长度问题的理想产品。

#### 特点

- 频率范围: 20-150MHz 时钟信号

- 较少的总线减少了连线尺寸和费用

- 内核供电电源 3.3V

- I0 供电电源 1.8V、3.3V 兼容

- 低功耗模式

- 支持 VGA、SVGA、XGA、SXGA

- 支持扩展频谱时钟产生

- 内部集成输入抖动滤波器

- 525Megabytes/sec 帯宽

- 减小 LVDS 摆幅来减小电磁干扰 (200mV 或 345mV LVDS 摆幅可供选择)

- PLL 不需要外部结构

- 遵循 TIA/EIA-644 LVDS 标准

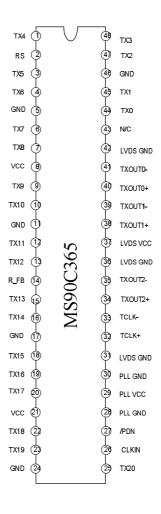

### 管脚定义

### MS90C365 管脚说明

| 管脚名              | 管脚序号               | 管脚类型    | 描述                         |

|------------------|--------------------|---------|----------------------------|

| TXOUTO-, TXOUTO+ | 40, 41             | LVDS 输出 | LVDS 差分数据输出                |

| TXOUT1-, TXOUT1+ | 38, 39             | LVDS 输出 |                            |

| TXOUT2-, TXOUT2+ | 34, 35             | LVDS 输出 |                            |

| TCLK+, TCLK-     | 32, 33             | LVDS 输出 | LVDS 差分时钟输出                |

| TXO ~ TX6        | 44,45,47,48,1,3,4  | 输入      | TTL 级数据输入。                 |

| TX7 ~ TX13       | 6,7,9,10,12,1315   | 输入      | 包括: 6 RED,6 GREEN,6 BLUE,3 |

| TX14 ~ TX20      | 16,18,19,20,22,23, | 输入      | 个控制信号(HSYNC, VXYNC, DE)    |

|                  | 25                 | 捌八      |                            |

| CLK IN           | 26                 | 输入      | TTL 级时钟输入。                 |

iSweek www.isweek.cn

公司名: 深圳市工采网络科技有限公司

电话: +86-0755-83279017-8007

地址: 广东省深圳市南山区高新南一道中国科技开发院3号楼16层

传真: + 86-0755-83279017-8007

邮箱: salesz@isweek.com

| /PDN     | 27            | 输入       | TTL 级输入。高:正常工作         |  |  |  |

|----------|---------------|----------|------------------------|--|--|--|

|          |               | 1107人    | 低: 低功耗                 |  |  |  |

| R_FB     | 14            | <br>  输入 | 选择有效边沿。                |  |  |  |

|          |               | 捌八       | 高:上升沿 低:下降沿            |  |  |  |

| RS       | 2             | 输入       | LVDS 摆幅控制(正常 RS=VCC,小  |  |  |  |

|          |               | 捌八       | 摆幅 RS=GND)             |  |  |  |

| VCC      | 8             | 电源       | TTL 级输入电源              |  |  |  |

| IOVCC    | 21            | I0 电源    | IO 口电源, 1.8V 和 3.3V 兼容 |  |  |  |

| GND      | 5,11,17,24,46 | 地        | TTL 级输入地               |  |  |  |

| LVDS VCC | 37            | 电源       | LVDS 输出电源              |  |  |  |

| LVDS GND | 31,36,42      | 地        | LVDS 输出地               |  |  |  |

| PLL VCC  | 29            | 电源       | PLL 电源                 |  |  |  |

| PLL GND  | 28,30         | 地        | PLL 地                  |  |  |  |

### 结构框图

# 推荐工作条件

电源电压 (VCC)

-0.3V - 4.0V

CMOS/TTL 输入电压

-0.3V - (VCC+0.3V)

CMOS/TTL 输出电压

-0.3V - (VCC+0.3V)

结点温度 +150°C

温度范围 -65° C - 150° C

MS90C365 1.9W

# Sweek www.isweek.cn

最大功耗 (25°C)

# 电学特性

| 符号                | 参数      | 条件                                                      | Min | Тур | Max      | Units |

|-------------------|---------|---------------------------------------------------------|-----|-----|----------|-------|

| $V_{\mathrm{IH}}$ | 输入高电平   |                                                         | 2.0 |     | $V_{CC}$ | V     |

| $V_{IL}$          | 输入低电平   |                                                         | GND |     | 0.8      | V     |

| $I_{IN}$          | 输入电流    | 0≪V IN≪VCC                                              |     |     | ±10      | uA    |

| $I_{PD}$          | 低功耗状态电流 | R_FB=V <sub>CC</sub> , V <sub>IH</sub> =V <sub>CC</sub> |     |     | 10       | uA    |

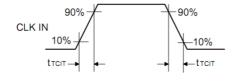

# 开关特性

| 符号                | 参数          |                    | Min    | Тур      | Max    | Units |

|-------------------|-------------|--------------------|--------|----------|--------|-------|

| T <sub>TCIT</sub> | 时钟信号过渡时间    |                    |        |          | 5. 0   | ns    |

| T <sub>TCP</sub>  | 时钟周期        |                    | 11.76  | T        | 50     | ns    |

| $T_{TCH}$         | 时钟高电平持续时间   |                    | 0. 35T | 0. 5T    | 0. 65T | ns    |

| T <sub>TCL</sub>  | 时钟低电平持续时间   |                    | 0. 35T | 0. 5T    | 0. 65T | ns    |

| T <sub>TS</sub>   | TTL 数据建立时间  |                    | 2.5    |          |        | ns    |

| T <sub>TH</sub>   | TTL 数据保持时间  |                    | 0      |          |        | ns    |

| $T_{LVT}$         | LVDS 信号转换时间 |                    |        | 0.6      |        | ns    |

| $T_{TCD}$         | 时钟输入与差分时钟信号 | 号延迟                |        | 2T/7+2.3 |        | ns    |

| T <sub>TDP1</sub> | 输出数据位 0     | 150MHz             | -0.2   | 0        | +0.2   | ns    |

| T <sub>TDP0</sub> | 输出数据位1      |                    |        | 0.95     |        | ns    |

| T <sub>TDP6</sub> | 输出数据位 2     |                    |        | 1. 90    |        | ns    |

| $T_{TDP5}$        | 输出数据位3      |                    |        | 2.86     |        | ns    |

| $T_{TDP4}$        | 输出数据位 4     |                    |        | 3. 81    |        | ns    |

| T <sub>TDP3</sub> | 输出数据位 5     |                    |        | 4. 76    |        | ns    |

| $T_{TDP2}$        | 输出数据位 6     |                    |        | 5. 71    |        | ns    |

| T <sub>TDP1</sub> | 输出数据位 0     | $100 \mathrm{MHz}$ | -0.2   | 0        | +0.2   | ns    |

| $T_{TDP0}$        | 输出数据位1      |                    |        | 1. 43    |        | ns    |

| T <sub>TDP6</sub> | 输出数据位 2     |                    |        | 2.86     |        | ns    |

| T <sub>TDP5</sub> | 输出数据位3      |                    |        | 4. 29    |        | ns    |

| $T_{TDP4}$        | 输出数据位 4     |                    |        | 5. 71    |        | ns    |

| T <sub>TDP3</sub> | 输出数据位 5     |                    |        | 7. 14    |        | ns    |

| T <sub>TDP2</sub> | 输出数据位 6     |                    |        | 8. 47    |        | ns    |

| T <sub>TDP1</sub> | 输出数据位 0     | 85MHz              | -0.2   | 0        | +0.2   | ns    |

| $T_{TDP0}$        | 输出数据位1      |                    |        | 1. 68    |        | ns    |

| T <sub>TDP6</sub> | 输出数据位 2     |                    |        | 3. 36    |        | ns    |

| T <sub>TDP5</sub> | 输出数据位3      |                    |        | 5. 04    |        | ns    |

| T <sub>TDP4</sub> | 输出数据位 4     |                    |        | 6. 72    |        | ns    |

| T <sub>TDP3</sub> | 输出数据位 5     |                    |        | 8. 40    |        | ns    |

| T <sub>TDP2</sub> | 输出数据位 6     |                    |        | 10.08    |        | ns    |

| $T_{TDP1}$        | 输出数据位 0     | 50MHz              | -0.2   | 0        | +0.2   | ns    |

| $T_{TDPO}$        | 输出数据位1      |                    |        | 2.86     |        | ns    |

|                    |         |          | 1    | 1      | 1    | 1  |

|--------------------|---------|----------|------|--------|------|----|

| T <sub>TDP6</sub>  | 输出数据位 2 |          |      | 5. 71  |      | ns |

| T <sub>TDP5</sub>  | 输出数据位3  |          |      | 8. 57  |      | ns |

| T <sub>TDP4</sub>  | 输出数据位 4 |          |      | 11. 42 |      | ns |

| T <sub>TDP3</sub>  | 输出数据位 5 |          |      | 14. 28 |      | ns |

| $T_{TDP2}$         | 输出数据位 6 |          |      | 17. 14 |      | ns |

| $T_{TDP1}$         | 输出数据位 0 | 35MHz    | -0.2 | 0      | +0.2 | ns |

| $T_{TDP0}$         | 输出数据位1  |          |      | 4. 08  |      | ns |

| T <sub>TDP6</sub>  | 输出数据位 2 |          |      | 8. 16  |      | ns |

| T <sub>TDP5</sub>  | 输出数据位3  |          |      | 12. 24 |      | ns |

| T <sub>TDP4</sub>  | 输出数据位 4 |          |      | 16. 33 |      | ns |

| T <sub>TDP3</sub>  | 输出数据位 5 |          |      | 20. 41 |      | ns |

| $T_{TDP2}$         | 输出数据位 6 |          |      | 24. 49 |      | ns |

| $T_{TDP1}$         | 输出数据位 0 | 20MHz    | -0.2 | 0      | +0.2 | ns |

| T <sub>TDP0</sub>  | 输出数据位1  |          |      | 7. 14  |      | ns |

| T <sub>TDP6</sub>  | 输出数据位 2 |          |      | 14. 28 |      | ns |

| T <sub>TDP5</sub>  | 输出数据位3  |          |      | 21.42  |      | ns |

| T <sub>TDP4</sub>  | 输出数据位 4 |          |      | 28. 57 |      | ns |

| T <sub>TDP3</sub>  | 输出数据位 5 |          |      | 35. 71 |      | ns |

| T <sub>TDP2</sub>  | 输出数据位 6 |          |      | 42.86  |      | ns |

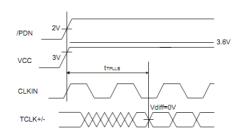

| T <sub>TPLLS</sub> | 锁相环设置时间 | <u> </u> | _    | _      | 10   | ms |

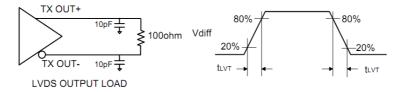

#### 直流特性

| 符号               | 参数              | 条件        | Min   | Тур  | Max   | Units |

|------------------|-----------------|-----------|-------|------|-------|-------|

| V <sub>OD</sub>  | 差分输出电压 (RS=VCC) |           | 250   | 345  | 450   | mV    |

|                  | 差分输出电压(RS=GND)  |           | 100   | 200  | 300   |       |

| △V <sub>OD</sub> |                 | DI -100 O |       |      | 35    | mV    |

| V <sub>OC</sub>  | 共模电压(RS=VCC)    | RL=100 Ω  | 1.125 | 1.25 | 1.375 | V     |

|                  | 共模电压(RS=GND)    |           |       | 1.20 |       |       |

| △V <sub>OC</sub> |                 |           |       |      | 35    | mV    |

| $I_{0Z}$         |                 | /PDN=OV   |       |      | ±10   | uA    |

# 电源电流

| 符号                | 参数              | 条件       | Тур | Max | Units |

|-------------------|-----------------|----------|-----|-----|-------|

| Icctg             |                 | f=20MHz  | 18  |     | mA    |

|                   |                 | f=35MHz  | 25  |     | mA    |

|                   | 供电电流            | f=50MHz  | 28  |     | mA    |

|                   | 16 Grayscale    | f=85MHz  | 30  |     | mA    |

|                   |                 | f=100MHz | 33  |     | mA    |

|                   |                 | f=150MHz | 36  |     | mA    |

| I <sub>CCTP</sub> | Power down 时的电流 | /PDN=OV  | 21  |     | uA    |

iSweek www.isweek.cn

公司名: 深圳市工采网络科技有限公司

地址: 广东省深圳市南山区高新南一道中国科技开发院3号楼16层

电话: +86-0755-83279017-8007

传真: +86-0755-83279017-8007

邮箱: salesz@isweek.com

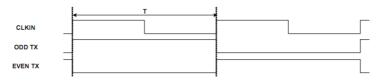

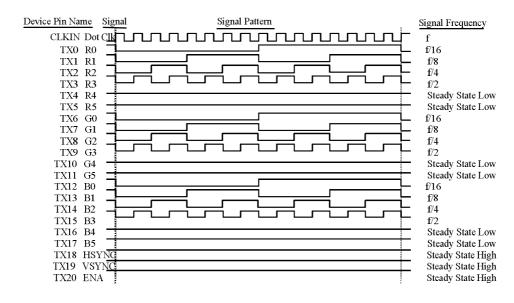

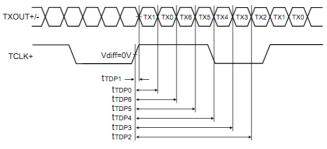

#### 交流时序图

图 1.测试模板 "Worst Case Pattern"

图 2.测试模板"16 Grayscale Test Pattern"

图 3.TTL 输入

图 4.LVDS 输出

$V_{diff} = (TXOUT+) - (TXOUT-)$

#### 图 5.锁相环设置时间

#### 图 6. 发送器状态

Vdiff= (TXOUT+) - (TXOUT-), ······ (TCLK+) - (TCLK-)

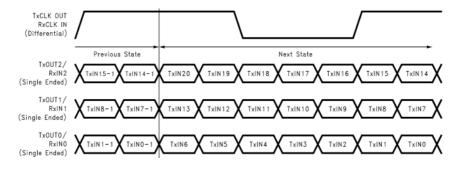

### 图 7. 并行 TTL 输入数据与 LVDS 输出数据匹配关系

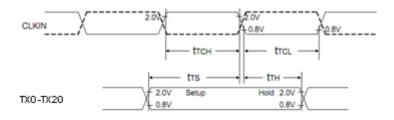

图 8. 上升、下降时间与高电平、低电平保持时间

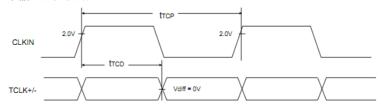

图 9. 输入时钟与输出时钟间延迟

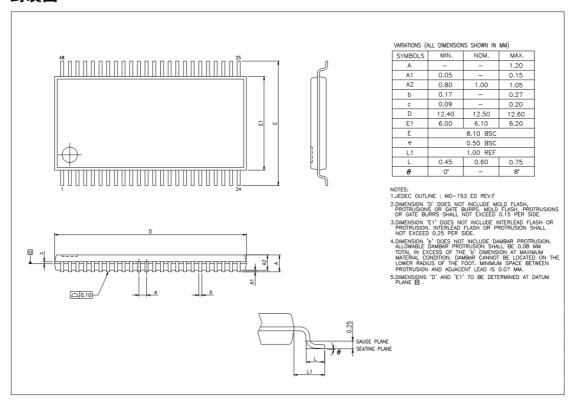

### 封装图